IBM Demos Transistor with Liquid Nitrogen Cooling

Liquid nitrogen boils at just 77 Kelvins (-196 °C). Cooling electronics to this frigid temperature could boost performance, but today’s transistors aren’t designed with cryogenic temperatures in mind. At the 2023 IEEE International Electron Device Meeting (IEDM) held in San Francisco earlier in December, IBM researchers demonstrated the first advanced CMOS transistor optimized for liquid nitrogen cooling.

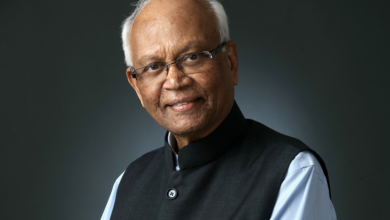

Nanosheet transistors split the channel into a stack of thin silicon sheets, which are completely surrounded by the gate. “Nanosheet device architecture enables us to fit 50 billion transistors in a space roughly the size of a fingernail,” says Ruqiang Bao, a senior researcher at IBM. The transistors are poised to replace current FinFET technology, and they are used in IBM’s first 2-nanometer prototype processor. Nanosheet technology is the next step in scaling down logic devices; pairing the tech with liquid nitrogen cooling could lead to even better performance.

The researchers found that operating at 77 K doubled device performance, compared with operating at roughly room temperature conditions of 300 K. Low-temperature systems, Bao says, offer two key advantages: less charge carrier scattering and lower power. Reducing scattering reduces resistance in the wires and lets electrons move through the device more quickly. Combined with lower power, devices can drive a higher current at a given voltage.

Cooling the transistor to 77 K also offers greater sensitivity between the device’s “on” and “off” positions, with a smaller change in voltage needed to switch from one state to the other. This can significantly lower power consumption. Lowering the power supply, in turn, could help scale down chip size by reducing the transistor width. However, a transistor’s threshold voltage—the voltage needed to create a conducting channel between the source and drain, or switch to the “on” position—increases as temperature decreases, presenting a key challenge.

It’s difficult to lower the threshold voltage with today’s manufacturing technology, so the IBM researchers opted for a new approach integrating two different metal gates and dual dipoles. CMOS technologies consist of pairs of n-type and p-type transistors, which are doped with electron donors and acceptors, respectively. The researchers engineered their CMOS chips to form dipoles at the interface of both the n- and p-type transistors by adding different metal impurities to each. The addition lowers the energy needed to move electrons across the band edge, making for more efficient transistors.

IEEE Spectrum