New Transistors Might Need a Different Cut of Silicon

The wafers of silicon that ultimately become the chips in your smartphone consists of a single crystal. But that crystal has many faces, and it matters which of those faces is at the surface, where transistors are made. According to research presented last month at the 2023 IEEE International Electron Device Meeting, the industry might not be using the best crystal orientation for upcoming devices. By changing the crystal orientation, a team at IBM Research achieved as much as a doubling of the speed of positive charge through transistors, though it came at the cost of a slight slowdown for negative charge.

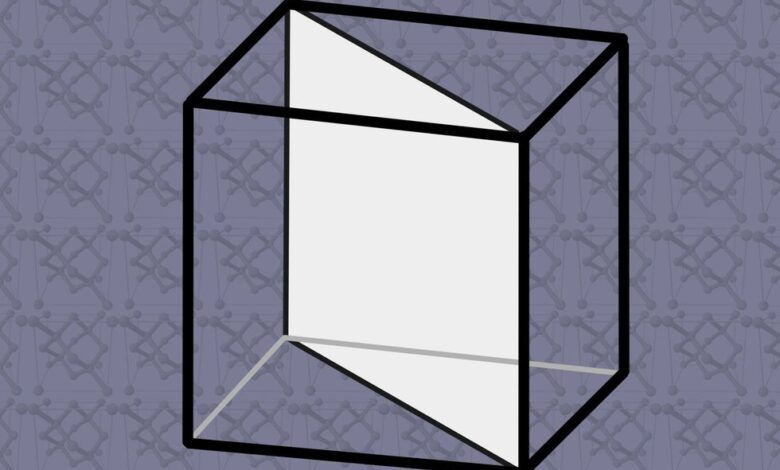

Crystals can be reduced to a unit structure that’s infinitely repeatable. For silicon it’s a cube that looks like it’s got a diamond stuck inside it. There are silicon atoms at each corner of the cube as well as at the center of each face and four more atoms within the cube’s interior. Today’s transistors, FinFETs mostly, are built on silicon where the top of that cube is the surface of the wafer. Experts call that crystal orientation “001.” Silicon wafers with the 001 orientation “are used in many advanced logic technologies, including in IBM’s 2 nanometer chip technology,” says IBM Research’s Shogo Mochizuki.

But Mochizuki and his colleagues say that as chipmakers transition to the next type of transistor, the nanosheet or gate-all-around device, they might get better results if instead they used the “110” orientation instead. That’s essentially a slice vertically through the cube.

Why would that make any difference? It has to do with how fast charge can travel through the silicon lattice. In the CMOS circuits that make up logic chips, both electrons and holes—positively charged electron vacancies—must flow. Generally, electrons are the zippier variety, so the relatively pokey mobility of holes is a limiting factor when chipmakers design ever smaller transistors. And it’s already known that holes move faster when traveling the 110 plane than the 001. The opposite is true for electrons, but the effect is smaller.

Today’s FinFETs already take advantage of the speedier travel in that plane. Although they are made using 001 silicon, the transistor’s channel region—the part where current flows when the device is on, or is blocked when it’s off—is a vertical fin of material in the 110 plane, perpendicular to the silicon surface. But in nanosheets, current has to flow through structures that are parallel to the silicon surface, in the hole-slowing 001 plane.

Mochizuki’s team constructed matching pairs of nanosheet transistors on both 001 and 110 silicon wafers. Both types of transistors—hole-conducting pFETs and electron-conducting nFETs—were present. In addition to the different crystal orientations, the transistors had a variety of different traits to test: Some had thin sheets, some thicker; some had long channels, some shorter. The110 pFETs outperformed their 001 brethren, though the magnitude of the effect sometimes differed according to the thickness of the silicon nanosheets. As expected, the nFETs worked slightly worse in 110 silicon. But the boost to the pFET performance is enough to make up for that, the researchers suggest.

Don’t look for industry to quickly switch to 110 silicon. “Technically, it is possible,” says Naoto Horiguchi, CMOS device technology program director at Belgium-based Imec. But there are enough differences in the way that layers of silicon and silicon germanium are grown on the different crystal orientations that it would “require careful engineering.”

Mochizuki says IBM plans to find a way to reduce the ill-effects of the alternative orientation on electron conduction. Additionally, the team will explore 110’s silicon’s use in 3D-stacked nanosheet transistors called complementary FETs (CFETs). This device architecture typically stacks an nFET on top of a pFET to cut down the size of logic circuits. Such stacked devices are expected roll out within ten years, and all three advanced logic chip manufacturers reported prototype CFETs last month at IEDM. Mochizuki says the IBM team may try building the pFET part from 110 silicon and the nFET from 001.

IEEE Spectrum